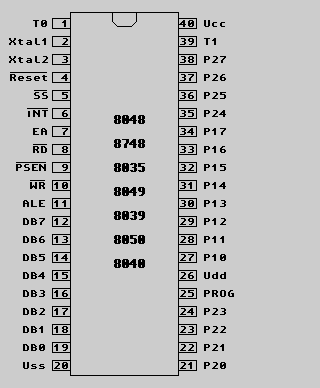

Rozkład wyprowadzeń 8048

Opis wyprowadzeń:

Sygnał Numer końcówki Funkcja DB0-DB7 12-19 - przy pracy bez zewnętrznej pamięci programu lub danych: 8-bitowy, dwukierunkowy port wejcia-wyjcia

- przy pracy z zewnętrznš pamięciš programu lub danych: multipleksowana magistrala adresowa lub danych P10-P17

(Port 1) 12-19 8-bitowy port we-wy P20-P23

P24-P27

(Port 2) 21-24

35-38 8-bitowy port we-wy

-przy pracy z zewnętrznš pamięciš programu: bity P20-P23 sš wyjciem magistrali adresowej

- przy współpracy z ekspanderem 8243: bity P20-P23 pełniš funkcję 4-bitowej magistrali danych T0

(Test 0) 1 - wejcie którego stan może być testowany za pomocš rozkazu skoku warunkowego (JT0, JNT0)

- po wykonaniu rozkazu ENT0 CLK, wyjcie sygnału zegarowego

- używany podczas programowania pamięci EPROM T1

(Test 1) 39 - wejcie którego stan może być testowany za pomocš rozkazu skoku warunkowego (JT1, JNT1)

- po wykonaniu rozkazu STRT CNT, wejcie sygnału zegarowegodla wewnętrznego układu czasowo licznikowego /INT

(Interput) 6 - wejcie, którego stan może być testowany za pomocš rozkazu skoku warunkowego (JNI)

- wejcie przerywajšce (aktywny stan niski) /RD

(Read) 8 wyjcie sterujšce; odczytywanie z zewnętrznej pamięci danych (aktywny stan niski) /WR

(Write) 10 wyjcie sterujšce; zapisywanie do zewnętrznej pamięci danych (aktywny poziom niski) /PSEN

(Program store enable) 9 wyjcie sterujšce; odczytywanie z zewnętrznej pamięci programu (aktywny stan niski) ALE

(Adres latch enable) 11 - wyjcie sygnału zegarowego o częstotliwoci Fxtal/15

- przy pracy z pamięciš zewnętrznš; wyjcie sterujšce - strob adresu wysłanego na BUS PROG 25 - wyjcie sygnału sterujšcego do współpracy z ekspanderem 8243

- wejcie dla impulsu programujšcego (18V) przy programowaniu pamięci EPROM /RESET 4 - wejcie sygnału zerujšcego (aktywny poziom niski)

- używane podczas obniżonego poboru mocy

- strob adresu przy programowaniu pamięci EPROM

- strob adresu przy odczytywaniu wewnętrznej pamięci programu /SS 5 wejcie sterujšce pracy krokowej, wymuszajšce wstrzymanie pracy procesora EA

(External access) 7 - wejcie wymuszajšce pobieranie wszystkich rozkazów z zewnętrznej pamięci programu

- EA=+18V - ustawia tryb programowania i weryfikacji pamięci EPORM

- EA=+12V - ustawia tryb odczytywania wewnętrznej pamięci programu XTAL1 2 - pierwsza końcówka do przyłšczenia oscylatora kwarcowego

- wejcie sygnału taktujšcego XTAL2 3 druga końcówka do przyłšczenia oscylatora kwarcowego Ucc 40 +5V - zasilanie Udd 26 +5V w czasie normalnej pracy

+21V w czasie programowania EPROM

zasilanie rezerwowe w stanie obniżonego poboru mocy Uss 20 masa (0V)

Powrót

Darmowy hosting zapewnia PRV.PL

- przy pracy z zewnętrznš pamięciš programu lub danych: multipleksowana magistrala adresowa lub danych

(Port 1)

P24-P27

(Port 2)

35-38

-przy pracy z zewnętrznš pamięciš programu: bity P20-P23 sš wyjciem magistrali adresowej

- przy współpracy z ekspanderem 8243: bity P20-P23 pełniš funkcję 4-bitowej magistrali danych

(Test 0)

- po wykonaniu rozkazu ENT0 CLK, wyjcie sygnału zegarowego

- używany podczas programowania pamięci EPROM

(Test 1)

- po wykonaniu rozkazu STRT CNT, wejcie sygnału zegarowegodla wewnętrznego układu czasowo licznikowego

(Interput)

- wejcie przerywajšce (aktywny stan niski)

(Read)

(Write)

(Program store enable)

(Adres latch enable)

- przy pracy z pamięciš zewnętrznš; wyjcie sterujšce - strob adresu wysłanego na BUS

- wejcie dla impulsu programujšcego (18V) przy programowaniu pamięci EPROM

- używane podczas obniżonego poboru mocy

- strob adresu przy programowaniu pamięci EPROM

- strob adresu przy odczytywaniu wewnętrznej pamięci programu

(External access)

- EA=+18V - ustawia tryb programowania i weryfikacji pamięci EPORM

- EA=+12V - ustawia tryb odczytywania wewnętrznej pamięci programu

- wejcie sygnału taktujšcego

+21V w czasie programowania EPROM

zasilanie rezerwowe w stanie obniżonego poboru mocy